Nanochip Solution south india Academic partner

Access to cutting edge design tools and process technology is key to enhancing the skills of today's engineer. We are the exclusive partner to Synopsys for the distribution of IC Design tools to Academia.

We understand that academia is bent more towards research and innovation and access to advance technologies is key to further this vision. Nanochip solution takes pride in working closely with department heads, Research scholars and college managements to adopt latest technology within the academic set up and use it successfully to design and innovative.

Bundles : University Bundles for the year 2017 - 18

VLSI BUNDLEView more..

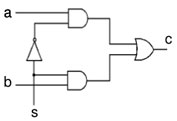

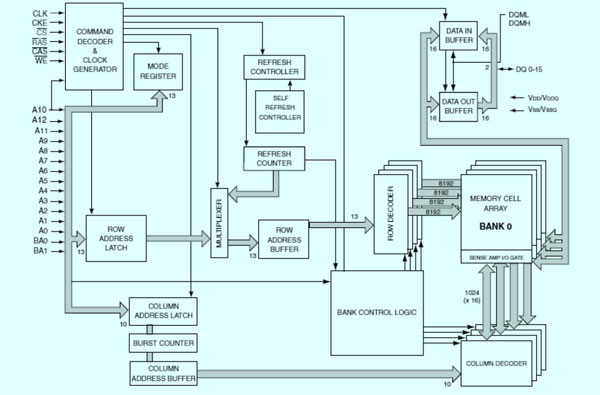

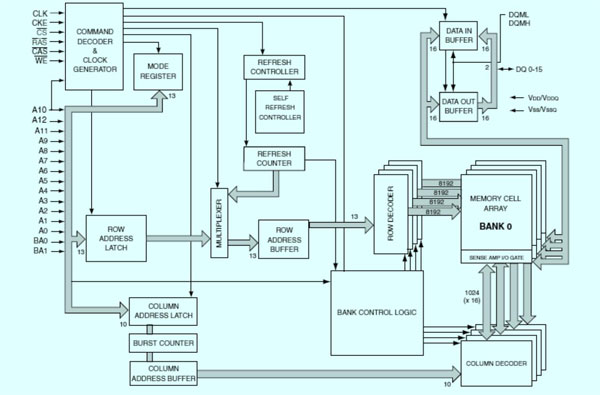

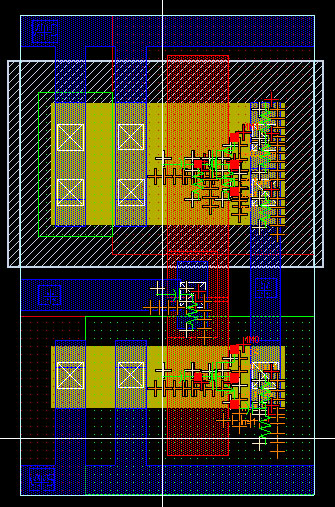

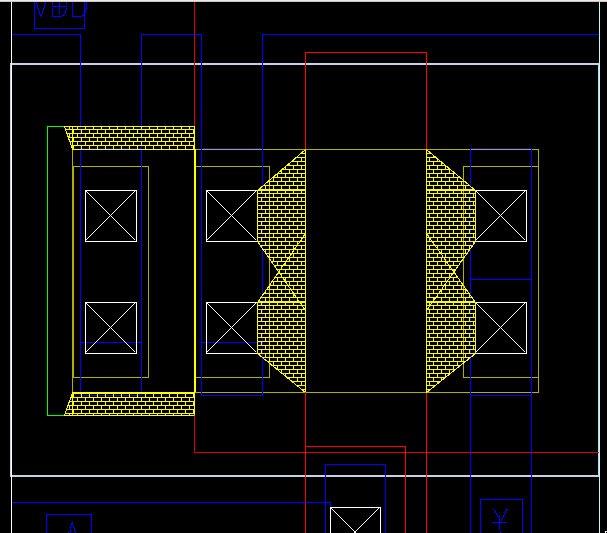

- ASIA PAC FRONTEND UNIVERSITY BUNDLE

- ASIA PAC BACKEND UNIVERSITY BUNDLE

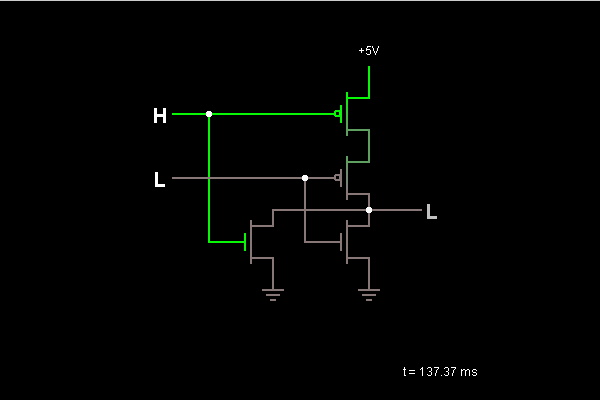

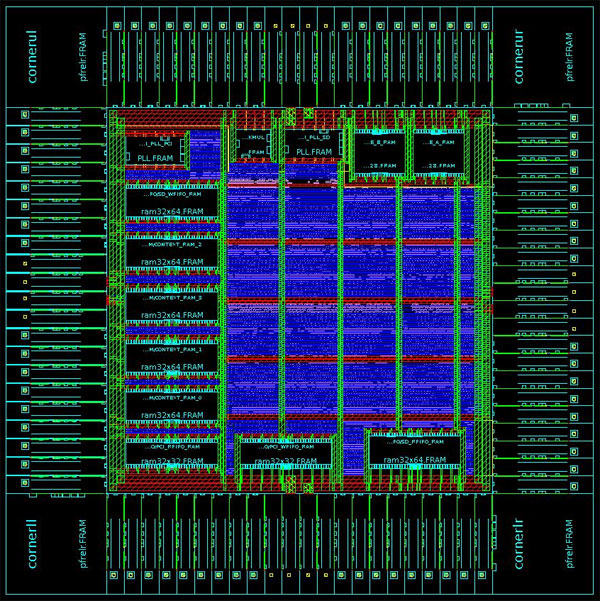

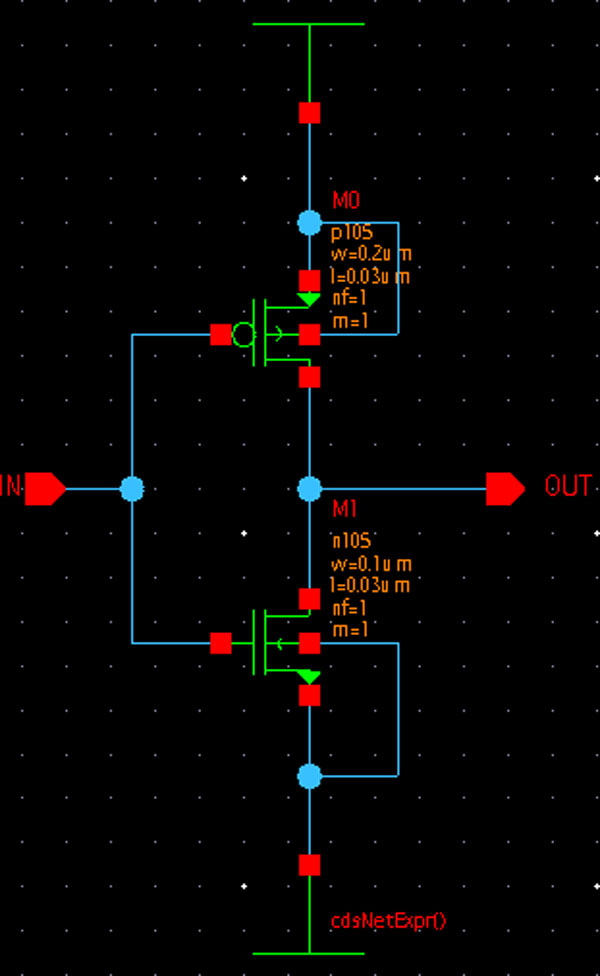

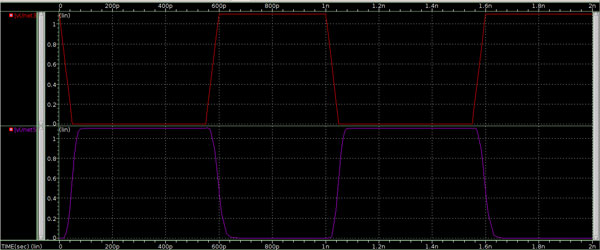

- ASIA PAC FULLCUSTOM UNIVERSITY BUNDLE

- SPYGLASS UNIVERSITY BUNDLE

SENTAURUS TCAD BUNDLEView more..

- ASIA PAC ADVANCED TCAD UNIVERSITY BUNDLE

- ASIA 2D TCAD UNIVERSITY BUNDLE

SABER RD BUNDLEView more..

- ASIA PAC SABER UNIVERSITY BUNDLE

Tool Planner

-

Select the design methodology you are interested in

-

Tools used as part of

-

Number of licence you are looking for ?

Support for university customers

Welcome

Your Support Engineer

Click here to ask Question